Digital Audio Sinewave Generator Based on Delta Modulation

Quote from KerimF on November 29, 2024, 9:05 amYour last remark helped me see the imperfection of the generated bit stream (for this frequency and many others).

I expected to also see 17 1's at the zero crossing of the positive slope/edge. I didn't see them.

So, I am revising the code to fix this imperfection.

Your last remark helped me see the imperfection of the generated bit stream (for this frequency and many others).

I expected to also see 17 1's at the zero crossing of the positive slope/edge. I didn't see them.

So, I am revising the code to fix this imperfection.

Quote from KerimF on December 21, 2024, 4:37 pmPlease note that the code in DSSaudioGenerator_v1.zip which was attached to post #4 had two serious bugs.

These two bugs are fixed in DDSSaudioGenerator_v2.zip which includes:

DDSSaudioGenerator_simu_v2.asm [8 MHz, its frequencies are doubled if 16 MHz ]

DDSSaudioGenerator_simu_v2.hex

DDSSaudioGenerator_simu_v2.lst

DDSSaudioGenerator_v2_hi.sim1

DDSSaudioGenerator_v2_lo.sim1

DDSSaudioGenerator_v2.png

DDSS_Bits_Frequencies_v2.txt

and

DDSSaudioGenerator_real_v2.asm

(If internal 8 MHz, lo-fuses= 0x24, hi-fuse= 0xD1)

(If external 8 MHz, lo-fuses= 0x28, hi-fuse= 0xD1)

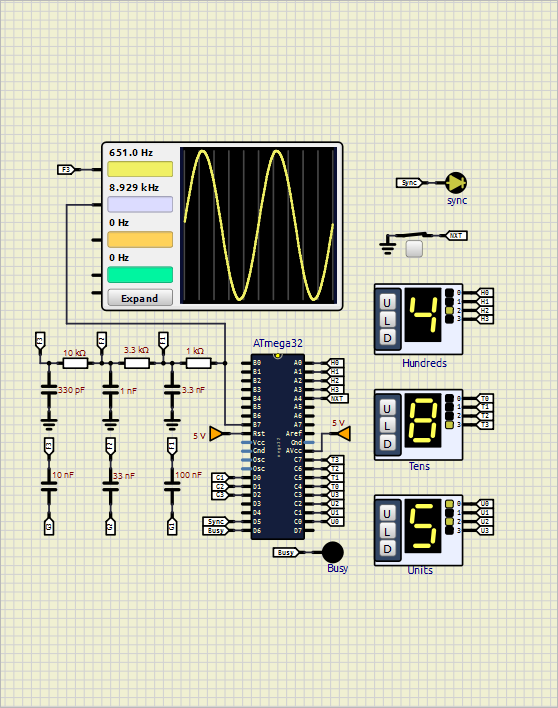

The code, tested with SimulIDE_1.2.0-RC1_Win32, consists of 3 parts:

Part_1: It generates the table, in SRAM, of sinewave whose bits/cycle, Nbits, is known [the lowest Nbits=96, the highest Nbits=3088, see DDSS_Bits_Frequencies_v2.txt]. Its algorithm is somehow related to CORDIC algorithm.

Part_2: It generates the table, in SRAM, of the delta bits sequence [size=12 to 386 bytes] by using the internal sinewave table and a preset delta step for each Nbits. Its algorithm is based on the basic delta modulation (comparing then adding or subtracting for the next comparison).

Part_3: It outputs the delta bits sequence by reading its table in SRAM. There is a fast loop for the high band [delta clock = 2 MHz], and a slow loop for the low band [delta clock = 62,500 Hz, 2 MHz/32].

Since the size of the SRAM is only 2024 bytes, I had to divide the band of 485 frequencies to five sub-bands, each has its own paths in the code:

band_0, from 000 to 096 or 485 to 581 [Nbits=96 to 192]

band_1, from 097 to 193 or 582 to 678 [Nbits=194 to 386]

band_2, from 194 to 290 or 679 to 775 [Nbits=338 to 772]

band_3, from 291 to 387 or 776 to 872 [Nbits=776 to 1544]

band_4, from 388 to 484 or 873 to 969 [Nbits=1552 to 3088]

Notes:

[1] I renamed DSS to DDSS, for Digital Delta Sinewave Synthesis, to avoid the confusion, since DSS could also mean Digital Sinewave Synthesis.

[2] There are two *.asm files; one for simulIDE simulation, DDSSaudioGenerator_simu_v2.asm, and one for a real prototype, DDSSaudioGenerator_real_v2.asm. I noticed that the pins of the thumbwheel in SimulIDE are open (not connected to the common pin) when set to 0. They are shorted if real one. (See lines 2609 and 2615 of the assembly code.)

[3] There are two *.sim1; one for the high band [Frequency indexes from 000 to 484], DDSSaudioGenerator_v2_hi.sim1, and one for the low band [Frequency indexes from 485 to 969], DDSSaudioGenerator_v2_lo.sim1. The reason for which there are two *.sim1is the 2 different sets of capacitors in the schematic; 3 for each band.

Naturally this project is about an experimental circuit, hardware and firmware, to introduce the concept of DDSS. In real applications, there are no thumbwheels and a switch. There will be a second MCU (connected to the DDSS generator via a serial protocol) to run all the functions, other than generating the sine waves, needed by the application and the user. I am still working on it (though very slowly since my city has 2/24 mains AC only) with the hope I will build a simple practical generator, for audio in the least.

For instance, I think it is very clear now that the code of the DDS concept, Direct Digital Synthesis, is much easier than of the DDSS. Only the DDS hardware, like of any parallel DAC, is not as simple as of the DDSS which is a serial one.

Please note that the code in DSSaudioGenerator_v1.zip which was attached to post #4 had two serious bugs.

These two bugs are fixed in DDSSaudioGenerator_v2.zip which includes:

DDSSaudioGenerator_simu_v2.asm [8 MHz, its frequencies are doubled if 16 MHz ]

DDSSaudioGenerator_simu_v2.hex

DDSSaudioGenerator_simu_v2.lst

DDSSaudioGenerator_v2_hi.sim1

DDSSaudioGenerator_v2_lo.sim1

DDSSaudioGenerator_v2.png

DDSS_Bits_Frequencies_v2.txt

and

DDSSaudioGenerator_real_v2.asm

(If internal 8 MHz, lo-fuses= 0x24, hi-fuse= 0xD1)

(If external 8 MHz, lo-fuses= 0x28, hi-fuse= 0xD1)

The code, tested with SimulIDE_1.2.0-RC1_Win32, consists of 3 parts:

Part_1: It generates the table, in SRAM, of sinewave whose bits/cycle, Nbits, is known [the lowest Nbits=96, the highest Nbits=3088, see DDSS_Bits_Frequencies_v2.txt]. Its algorithm is somehow related to CORDIC algorithm.

Part_2: It generates the table, in SRAM, of the delta bits sequence [size=12 to 386 bytes] by using the internal sinewave table and a preset delta step for each Nbits. Its algorithm is based on the basic delta modulation (comparing then adding or subtracting for the next comparison).

Part_3: It outputs the delta bits sequence by reading its table in SRAM. There is a fast loop for the high band [delta clock = 2 MHz], and a slow loop for the low band [delta clock = 62,500 Hz, 2 MHz/32].

Since the size of the SRAM is only 2024 bytes, I had to divide the band of 485 frequencies to five sub-bands, each has its own paths in the code:

band_0, from 000 to 096 or 485 to 581 [Nbits=96 to 192]

band_1, from 097 to 193 or 582 to 678 [Nbits=194 to 386]

band_2, from 194 to 290 or 679 to 775 [Nbits=338 to 772]

band_3, from 291 to 387 or 776 to 872 [Nbits=776 to 1544]

band_4, from 388 to 484 or 873 to 969 [Nbits=1552 to 3088]

Notes:

[1] I renamed DSS to DDSS, for Digital Delta Sinewave Synthesis, to avoid the confusion, since DSS could also mean Digital Sinewave Synthesis.

[2] There are two *.asm files; one for simulIDE simulation, DDSSaudioGenerator_simu_v2.asm, and one for a real prototype, DDSSaudioGenerator_real_v2.asm. I noticed that the pins of the thumbwheel in SimulIDE are open (not connected to the common pin) when set to 0. They are shorted if real one. (See lines 2609 and 2615 of the assembly code.)

[3] There are two *.sim1; one for the high band [Frequency indexes from 000 to 484], DDSSaudioGenerator_v2_hi.sim1, and one for the low band [Frequency indexes from 485 to 969], DDSSaudioGenerator_v2_lo.sim1. The reason for which there are two *.sim1is the 2 different sets of capacitors in the schematic; 3 for each band.

Naturally this project is about an experimental circuit, hardware and firmware, to introduce the concept of DDSS. In real applications, there are no thumbwheels and a switch. There will be a second MCU (connected to the DDSS generator via a serial protocol) to run all the functions, other than generating the sine waves, needed by the application and the user. I am still working on it (though very slowly since my city has 2/24 mains AC only) with the hope I will build a simple practical generator, for audio in the least.

For instance, I think it is very clear now that the code of the DDS concept, Direct Digital Synthesis, is much easier than of the DDSS. Only the DDS hardware, like of any parallel DAC, is not as simple as of the DDSS which is a serial one.

Uploaded files: