PIC12F683 CCP1 compare mode

Quote from Christian on January 3, 2026, 12:02 pmHello again,

Also I can see a strange behaviour with CCP1 compare mode, still with 12F683 PIC.

I use the following register to toggle CCP1 pin (GP2) :

1000 = Compare mode, set output on match (CCP1IF bit is set)

1001 = Compare mode, clear output on match (CCP1IF bit is set)In debug mode, the toggle occurs every 93ms, which is expected with :

CCPR1H = 0b01011010; // CCPR1 = 0x5AEE = 23278 ticks = 0,025ms w/o prescaler CCPR1L = 0b11101110; // TMR1 registers will be compared with these registers T1CONbits.TMR1CS = 0; // TMR1 with internal Clock source FOSC/4 = 1µs T1CONbits.T1CKPS = 0b10; // Prescale 1:4 => 1 TMR1 tick = 4 µs

In SimulIDE, TMR1 never increments up to CCPR1 ; it seems CCP1IF flag is stuck to 1 and is never reset to 0, despite the code.

Hello again,

Also I can see a strange behaviour with CCP1 compare mode, still with 12F683 PIC.

I use the following register to toggle CCP1 pin (GP2) :

1000 = Compare mode, set output on match (CCP1IF bit is set)

1001 = Compare mode, clear output on match (CCP1IF bit is set)

In debug mode, the toggle occurs every 93ms, which is expected with :

CCPR1H = 0b01011010; // CCPR1 = 0x5AEE = 23278 ticks = 0,025ms w/o prescaler

CCPR1L = 0b11101110; // TMR1 registers will be compared with these registers

T1CONbits.TMR1CS = 0; // TMR1 with internal Clock source FOSC/4 = 1µs

T1CONbits.T1CKPS = 0b10; // Prescale 1:4 => 1 TMR1 tick = 4 µs

In SimulIDE, TMR1 never increments up to CCPR1 ; it seems CCP1IF flag is stuck to 1 and is never reset to 0, despite the code.

Uploaded files:

Quote from arcachofo on January 4, 2026, 1:44 pmHi, thanks for all the testing.

This and capture mode are hopefully fixed.

You can test it using this build (Windows64): SimulIDE_1.1.0-260104_test.zipLet me know if it doesn't work for you or there are more problems.

Hi, thanks for all the testing.

This and capture mode are hopefully fixed.

You can test it using this build (Windows64): SimulIDE_1.1.0-260104_test.zip

Let me know if it doesn't work for you or there are more problems.

Quote from Christian on January 4, 2026, 9:54 pmHello,

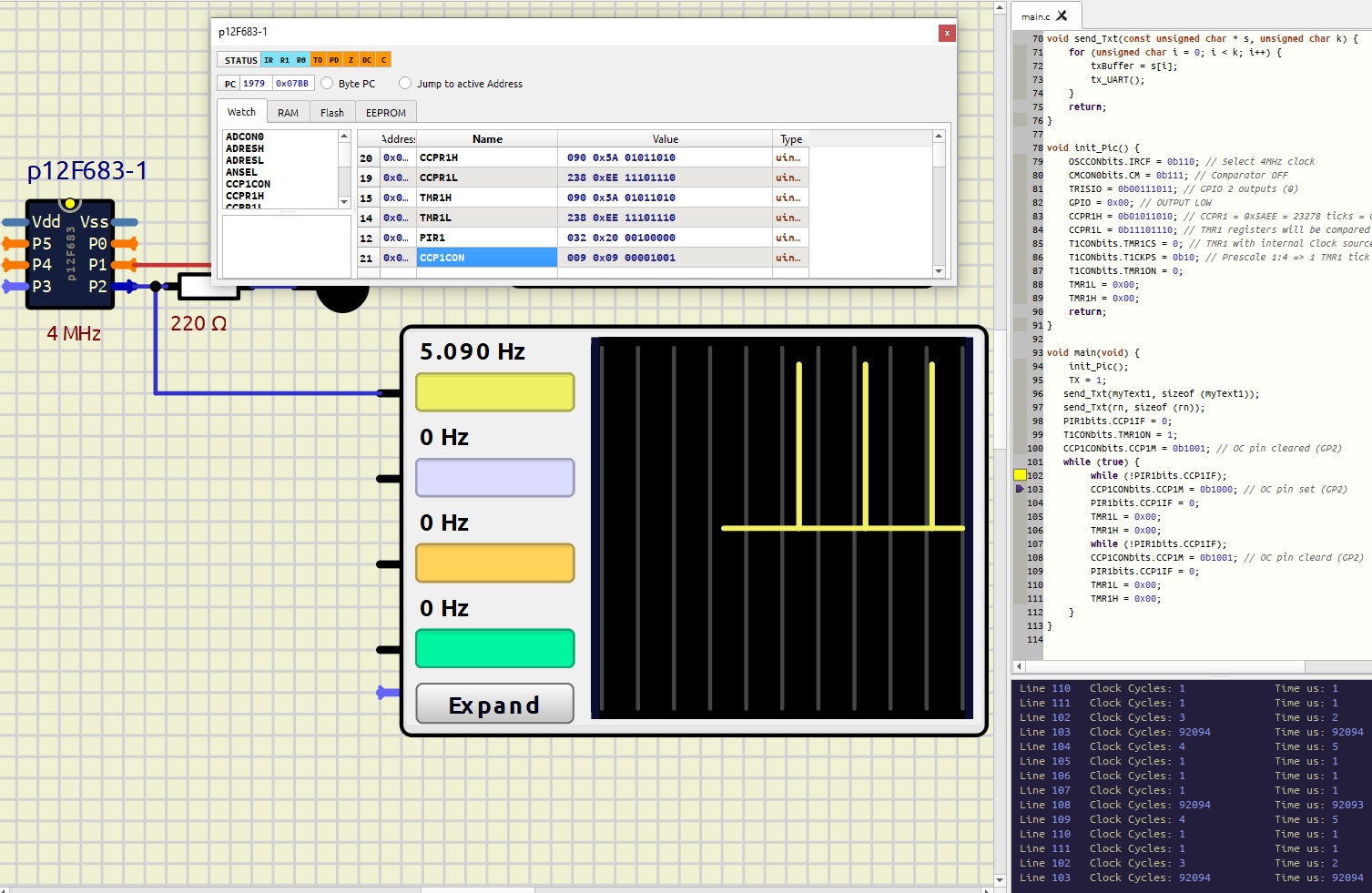

Thank you for your quick answer ! The period is good, but the duty cycle a bit strange ; see screenshot :

In debug mode, it seems like when CCP1M<3:0>: CCP Mode Select bits are set to :

1001 = Compare mode, clear output on match (CCP1IF bit is set)

it does not wait for CCP1IF bit set and immediately clear output.

When set to 1000, it does wait for CCP1IF bit and then set CCP1 pin.I changed the code for :

while (!PIR1bits.CCP1IF); PIR1bits.CCP1IF = 0; CCP1CONbits.CCP1M = 0b1000; // OC pin set (GP2) at next match TMR1L = 0x00; TMR1H = 0x00; while (!PIR1bits.CCP1IF); PIR1bits.CCP1IF = 0; CCP1CONbits.CCP1M = 0b1001; // OC pin cleared (GP2) at next match TMR1L = 0x00; TMR1H = 0x00;So timers are OK and match correctly, the CCP1IF bit is set accordingly, but maybe a problem with

0b1001mode ?

Or maybe my code is wrong or I did not understand the datasheet correctly.

Hello,

Thank you for your quick answer ! The period is good, but the duty cycle a bit strange ; see screenshot :

In debug mode, it seems like when CCP1M<3:0>: CCP Mode Select bits are set to :

1001 = Compare mode, clear output on match (CCP1IF bit is set)

it does not wait for CCP1IF bit set and immediately clear output.

When set to 1000, it does wait for CCP1IF bit and then set CCP1 pin.

I changed the code for :

while (!PIR1bits.CCP1IF);

PIR1bits.CCP1IF = 0;

CCP1CONbits.CCP1M = 0b1000; // OC pin set (GP2) at next match

TMR1L = 0x00;

TMR1H = 0x00;

while (!PIR1bits.CCP1IF);

PIR1bits.CCP1IF = 0;

CCP1CONbits.CCP1M = 0b1001; // OC pin cleared (GP2) at next match

TMR1L = 0x00;

TMR1H = 0x00;So timers are OK and match correctly, the CCP1IF bit is set accordingly, but maybe a problem with 0b1001 mode ?

Or maybe my code is wrong or I did not understand the datasheet correctly.

Quote from arcachofo on January 7, 2026, 1:31 pmYou are right, there is a problem with the output pin cleared every time the mode is changed.

I will upload new builds with fixes soon.

You are right, there is a problem with the output pin cleared every time the mode is changed.

I will upload new builds with fixes soon.